TSMC لیتوگرافی ۲ نانومتری N2 را با وعده ۵۶ درصد عملکرد بهتر از N5 معرفی کرد

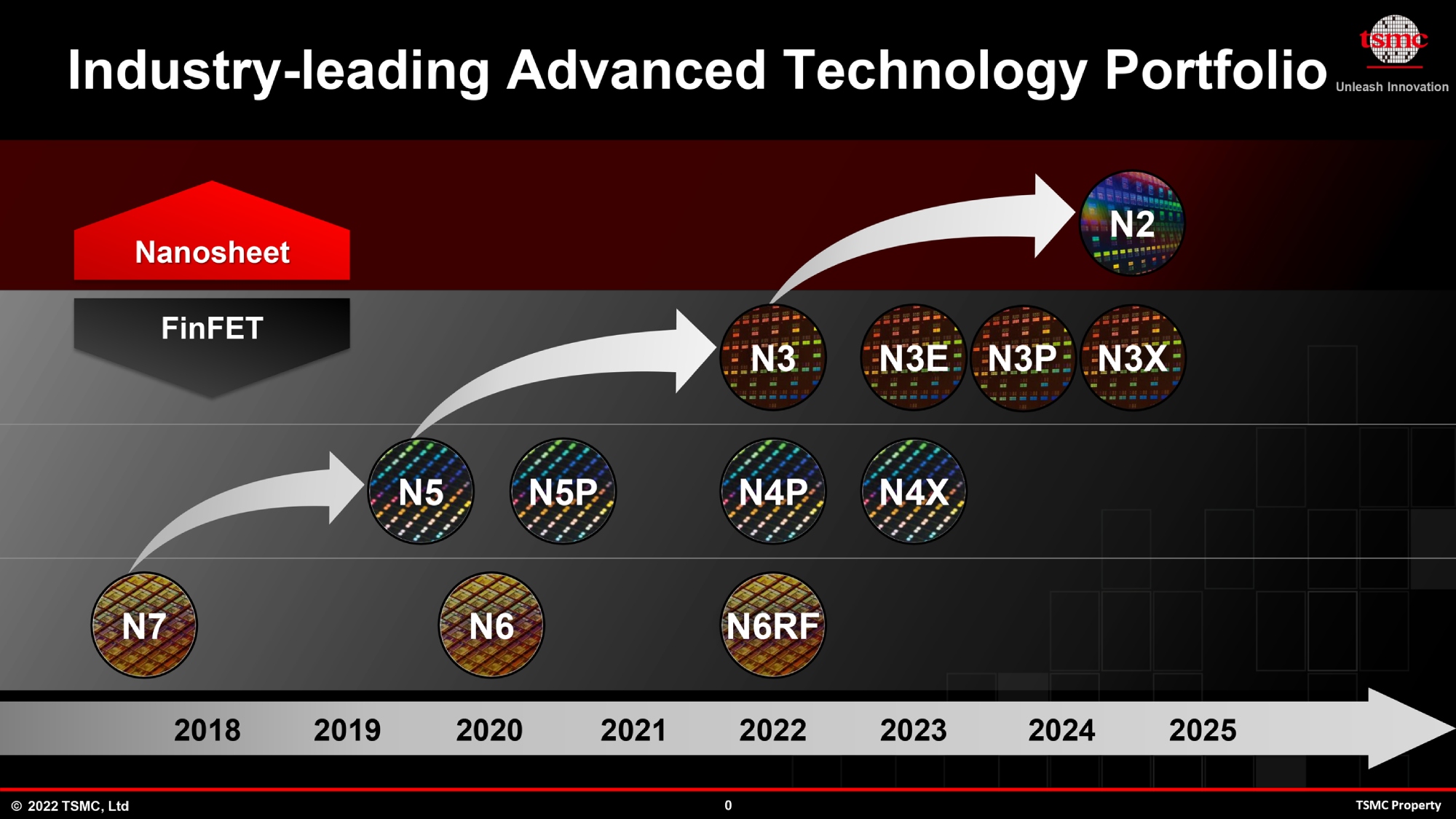

TSMC امروز بهطور رسمی از فناوری ساخت N2 (کلاس دو نانومتری) خود رونمایی کرد. این لیتوگرافی، اولین نمونهای است که از ترانزیستورهای اثر میدانی گیت (GAAFETs) استفاده میکند. این معماری ساخت جدید، مزایایی مثل عملکرد بهتر و قدرت بالا ارائه میکند. اولین تراشههای مبتنیبر لیتوگرافی مذکور سال ۲۰۲۵ تولید خواهند شد که البته ازنظر چگالی ترانزیستورها نسبت به نسلهای قبلی، تغییر چشمگیری در آنها دیده نخواهد شد.

به گزارش TomsHardware، معماری N2 شرکت TSMC بهعنوان یک پلتفرم کاملاً جدید، دو نوآوری اساسی بهارمغان میآورد: ترانزیستورهای نانوصفحه (که TSMC آن را GAAFET مینامد) و دوم بهره گرفتن از سیستم قدرت پشتی. این دومزیت هدف یکسانی برای بهبود عملکرد تراشهها در هر وات دنبال میکنند. ترانزیستورهای GAAFET از کانالهایی بهره میبرند که گیتها آنها را از چهار طرف احاطه کردهاند و همین ویژگی باعث کاهش هدررفت انرژی خواهد شد. علاوهبراین، میتوان کانالها را برای ارتقا جریان درایو و بهبود کارایی، افزایش داد یا برای به حداقل رساندن مصرف برق، آنها را فشردهتر کرد. ترانزیستورهای نانوصفحهای از سیستم انتقال قدرت پشتی برای ارائهی توان پردازشی بهتر و کاهش مصرف انرژی، بهره میبرند؛ فناوری جالبی که TSMC آن را یکی از بهترین راهکارهای جلوگیری از مقاومتها در انتهای خط (BEOL) میداند. شایان ذکر است معماری N2 شرکت TSMC بهطور گسترده از لیتوگرافی EUV استفاده میکند.

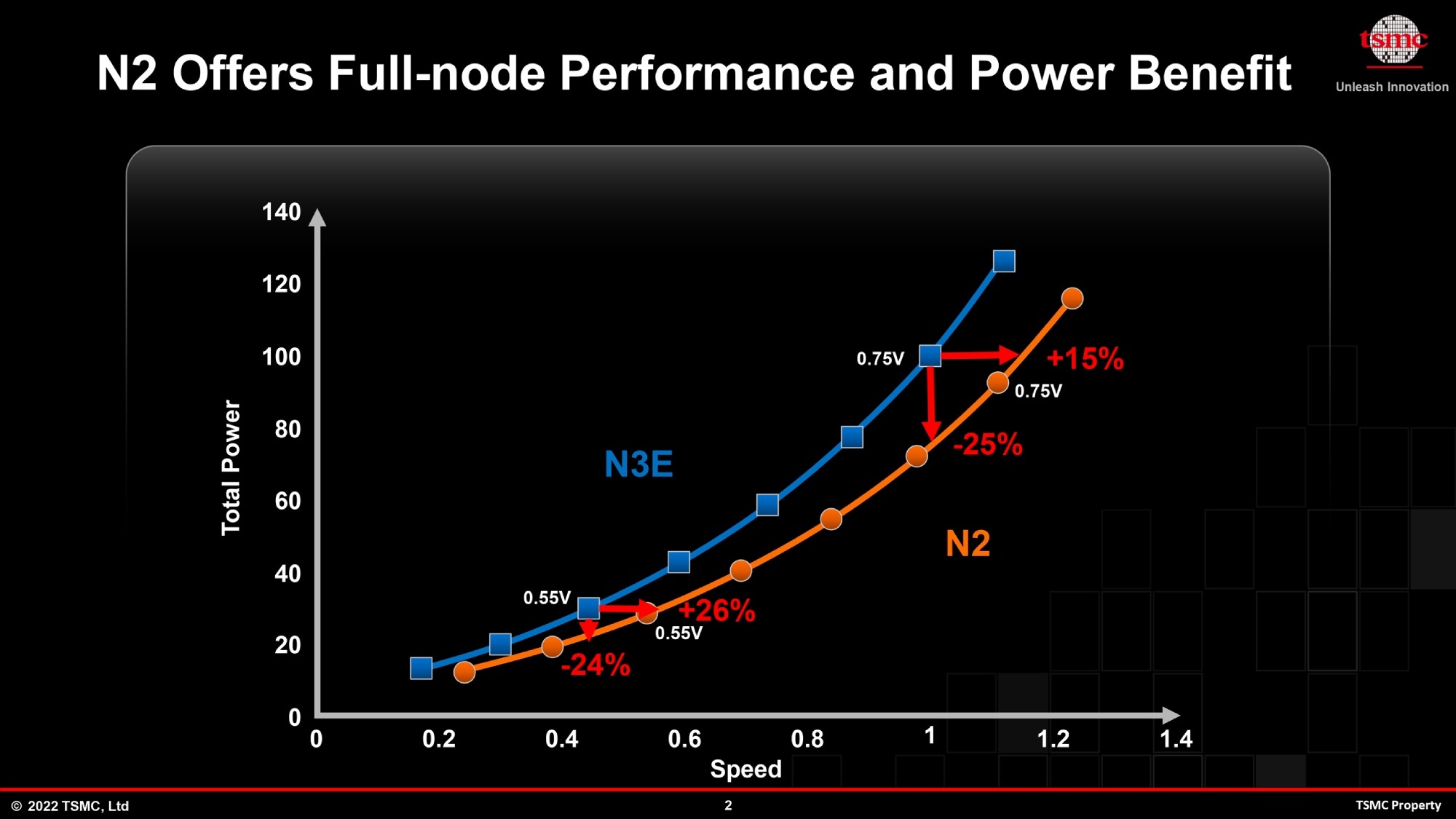

درواقع، هنگامی که صحبت از عملکرد و مصرف انرژی بهمیان آید، لیتوگرافی N2 مبتنیبر نانوصفحه TSMS میتواند ۱۰ تا ۱۵ درصد عملکرد بهتری نسبت به نسل قبلی خود ارائه دهد و درهمینحال، مصرف انرژی آن روی فرکانس مشابه بین ۲۵ تا ۳۰ درصد کمتر است. البته تعداد ترانزیستورهای این فرایند نسبت به فناوری N3E شرکت TSMC فقط ۱٫۱ برابر افزایش یافته است.

N2 درمقابل N3EN3E درمقابل N5N3 درمقابل N5N5 درمقابل N7بهبود سرعت با مصرف انرژی یکسان۱۰ تا ۱۵ درصد۱۸ درصد۱۰ تا ۱۵ درصد۱۵ درصدکاهش مصرف انرژی با فرکانس مشابهمنفی ۲۳ تا ۳۰ درصدمنفی ۳۴ درصدمنفی ۲۵ تا ۳۰ درصدمنفی ۳۰ درصدچگالی تراشهحدود ۱٫۱ برابر۱٫۳ برابر–تاریخ آغاز تولید انبوهنیمهی دوم ۲۰۲۵سهماهه دوم و سوم ۲۰۲۳نیمهی دوم ۲۰۲۲سهماهه دوم ۲۰۲۲

بهطورکلی، فرایند N3 TSMC باعث افزایش عملکرد و کاهش مصرف انرژی میشود، اما ازنظر چگالی تفاوت چشمگیری با فرایند نسل قبلی خود ندارد. درمقام مقایسه، چگالی تراشههای مبتنیبر N3E نسبت به N5 حدود ۱٫۳ برابر است. چگالی تراشه اساساً یک تراشهی فرضی را توصیف میکند که ۵۰ درصد از مدارهای منطقی، ۳۰ درصد از SRAM و ۲۰ درصد دیگر آن از مدارهای آنالوگ تشکیل شده است. طراحیهای مدرن SRAM فشرده هستند مقیاسپذیری کمی دارند؛ از این رو، یک تراشهی N2 درمقایسه با تراشههای مبتنیبر N3E، مقیاسپذیری متوسطی دارد. اگر N2 را با N3S که درواقع نسخهی بهینهسازیشدهی N3 است، مقایسه کنیم، نتیجه حتی کمتر چشمگیر خواهد بود.

با توجه به مشخصات ارائهشده، عملکرد تراشههای مبتنیبر معماری N2، با توان مصرفی یکسان تا ۵۶ درصد بهتر از تراشههای مبتنیبر معماری N5 خواهد بود.

ازآنجاکه مقیاس تراکم ترانزیستور در معماریهای جدید درحال کاهش است و استفاده از فناوریهای جدیدتر، هزینهی بیشتری برای تراشهسازان دارد، بستههای چندتراشهای در سال آینده، رایجتر خواهند شد زیرا توسعهدهندگان از آنها برای بهینهسازی طراحی و کاهش هزینههای خود بهره خواهند برد.

فرایند دو نانومتری TSMC برای برنامههای مختلف ازجمله سیستم-روی-چیپهای موبایلی، پردازندهای مرکزی با کارایی بالا و پردازندههای گرافیکی مورد استفاده قرار خواهد گرفت. بزرگترین تولیدکنندهی قراردادی تراشه جهان، درمیان ویژگیهای پلتفرم N2، به ادغام تراشهها اشاره میکند که احتمالاً یعنی میتوان از آن در بسیاری از حوزهها بهره گرفت.

همانطور که گزارش شده است، TSMC تولید انبوه تراشههای مبتنیبر لیتوگرافی دو نانومتری جدید را از نیمهدوم سال ۲۰۲۵ آغاز خواهد کرد. بنابراین با درنظر گرفتن مدتزمان چرخههای تولید نیمههادی فعلی، انتظار میرود تراشههای تجاری دونانومتری اواخر سال ۲۰۲۵ یا اوایل ۲۰۲۶ روانهی بازار شوند.

شرکت تایوانی TSMC رسماً از لینوگرافی جدید ۲ نانومتری (N2) خود رونمایی کرد. هدف از توسعهی این معماری، بهبود عملکرد و کاهش مصرف انرژی تراشهها است و اولین سیستم-روی-چیپهای مبتنیبر این فناوری نیز اواخر سال ۲۰۲۵ روانهی بازار خواهند شد.